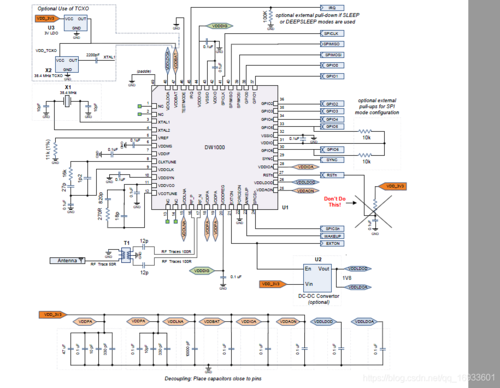

1.dw1000最小系统

2、器件选择建议:

射频前端

射频前端需要将差分信号转换成单端射频信号,一般使用HHM1595A1(俗称巴伦)。

频率参考

晶振一般选择38.4MHZ的TCXO,但是要注意加上LDO(TPS73601DBVR)

PLL环路滤波器

dw1000内部有两个锁相环电路,可生成基带处理时钟和RF本地震荡信号,每个PLL都需要外部环路滤波!

3.3V电源

dw1000有8个电源引脚,其中6个提供3.3V标称电压,其中2个可选择提供1.8V的较低电压。

每个3.3V电源至少需要一个去耦电容,VDDPA每个引脚需要三个去耦电容。

1.8V电源

两个电源引脚可以提供1.8V的较低电压。这需要使用外部DCDC转换器(LXDC2HL_18A)。DCDC转换器还需要额外的大容量电容,以及1.8VDW1000电源引脚的去耦电容。

限流电阻

VREF引脚一般接%1的电阻

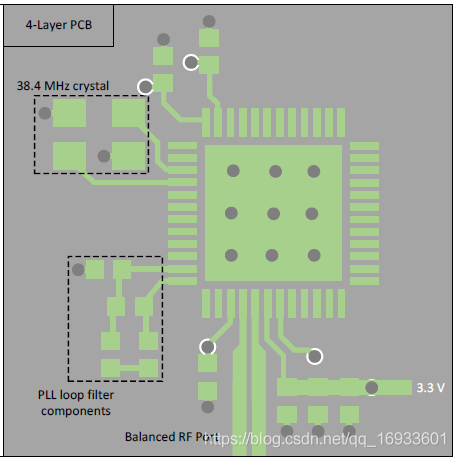

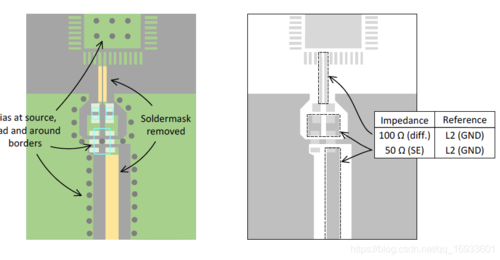

3.PCB设计

4层板建议的射频走线宽度如上所示。

射频走线尽可能短

射频走线的旁边的地线最好能通过过孔打穿,接到底层或者中间层的地平面上

过孔与射频信号线的距离不能太近,否则会严重影响射频信号质量

射频走线下方要注意不要有其他走线。

去耦电容必须靠近电源引脚放置,并且返回电流路径尽可能短。

射频走线周围禁止铺铜。

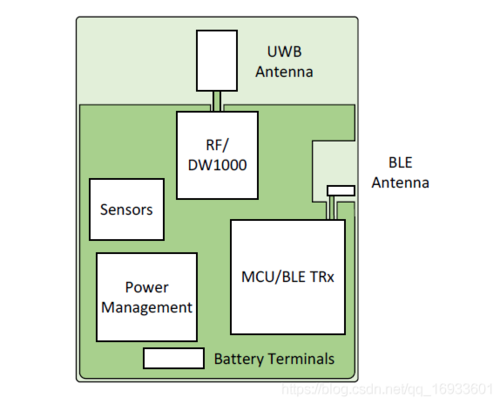

建议的器件布局示例

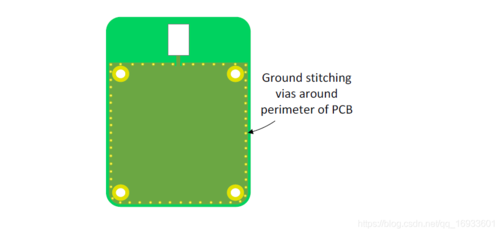

PCB周围接地过孔

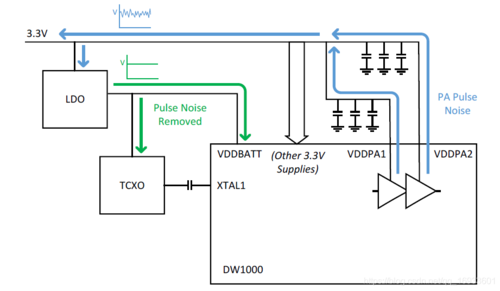

温控晶体振荡器(TCX0)可用作DW1000的频率参考。为了最大化参考信号的频谱纯度,TCX0电源引脚和DW1000VDDBATT|脚必须与噪声隔离。因此,建议使用LD0稳压器为TCX0和VDDBATT电源引脚供电。

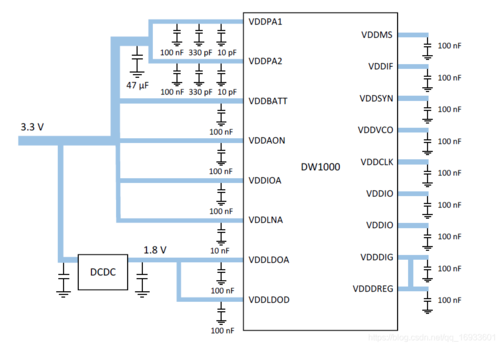

供电部分和去耦电容

DW1000有8个电源引脚,每个引脚都需要去耦电容,应尽可能靠近引脚放置。虽然片上LDO可以提供1.8V电压,但标准3.3V电源电压是必需的。外部DCDC转换器可以提供1.8V电压,以实现更高的功效。

在PCB布局中,3.3V电源可以使用过孔或者走线连接到DW1000,同时应该使用较窄的走线连接到去耦电容和引脚。47uF的大容量电容应靠近VDDPA引脚放置,将小容量电容放在最近的位置。1.8VDCDC转换器可为DW1000提供本地3.3V电源。

此外还需要外部电容来解耦DW1000的内部LDO稳压器输出。如下图所示。VDDDIG和VDDDREG是同一内部LDO稳压器的输出,它们应在PCB上连接在一起,以最大限度地减小去耦电容和内部电路之间的阻抗。

> 需要UWB相关软件源码,硬件PCB等资料的,可以加我QQ拉你进群,群文件免费获取。

共同学习,写下你的评论

评论加载中...

作者其他优质文章